我的项目

Contents

Current Project

Overview

建立一个嵌入式控制器芯片(SoC)的功能验证环境。这个芯片有embedded java processor,采用wishbone总线结构。

Verification Strategy

Productized Methodologies, Reuse, Block to System-Level Verification, Coverage

constraint random

There is no existing constraint solver in python, so each random constraint had to be written explicitly in test env.

coverage driven

code coverage

functional coverage

利用PSL中的cover来统计control based functional coverage

assertion based

用PSL作为assertion language。Simulation-Based ABV and FA are complementary technologies. Assertions written for use in FA can be also checked in simulation. Conversely, assertions written for use in simulation-based ABV can be used in FA. Other tools, such as emulation, may also be able to check the same assertions. During simulation, assertions act as monitors that check for expected behavior. The main issue with simulation-based assertion checking is that it requires test vectors, and is therefore, limited by the amount and quality of these test vectors.

Technologies and Tools

- Simulator采用Cadence的IUS54

- Debugger采用Novas的Debussy 5.4v7。

- Code Coverage analysis采用Cadence的Incisive Coverage Tool, 也就是hdlscore。

- Formal Verification -- Synopsys的Formality有人反映不是很稳定,前些日子看到Cadence推出了Incisive Formal Verifier,可惜的是,这个tool需要新的license feature Incisive_Formal_Verifier,并且还存在一些bug,所以只好暂时放弃。

- Emulation -- 这个项目里面采用了S2C公司的IPPorter,但是效果不是很好,姑且当作一个FPGA prototyping board来用吧!

FPGA Synthesis 采用 Synplicity的SynplifyPro8.1,需要注意的是产生license时,机器的时间需要临时修改成04-11-16。The bad thing is that batch mode is not supported with a node-locked license.

- ISE 7.1i Linux Version, serial number is 5919-8573-4470-4097

- Prototype Navigator from S2C is used for physical synthesis, current license is node-locked to asic4, will change it to floating license

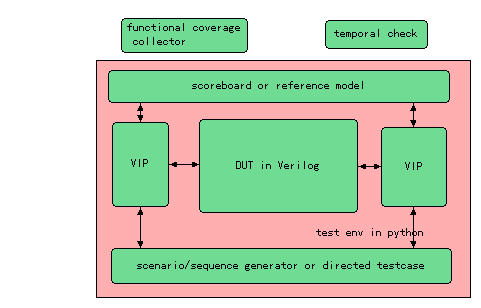

验证环境

ASIC simulation environment

FPGA simulation environment

This environment is developed to help locating bugs when something weird found in FPGA prototyping board. It has almost the same architecture as ASIC simulation environment, but with different tb_top and different internal memory structure.

FPGA prototyping board

- add32.edn, spram16kx8.edn, spram2kx32.edn, spram512x142.edn and spram70x32.edn is generated with ISE Core Generator, this project file is at sandbox/s25/FPGA/macro, command to regenerate these edn and .v files is coregen -b *.xco

- sprom16kx32.bmm is a manually coded file, the source information is from Xilinx datasheet and memory location information from the top_f3_ads1.pcf (physical constraint file) or use the ISE gui to open the top_f3_ads1.ncd and then find the information from the panel.

- sprom16kx32.mem is translated from vrom_verilog.hex by adding @0000 at the first line, and then replacing all RETURN with SPACE

top.edf is the synthesis output file with SynplifyPro

S2C Prototype Navigator will use ACE to do the Place&Route

Coverage Metrics

Code coverage analysis is mandatory in this project. Block/Path/Expression coverage are analysed. FSM coverage data is not analysed in this stage.

Functional Coverage is a relatively new concept in this project, so this coverage data collection and analysis is optional for each IP.

Regression

A seperate script written in python is used for regression. This script has the ability to run all of the test cases in a list file, and then generate a report summary file.

- regression without coverage

s25_regress.py -f <filename>

- regression with coverage

s25_regress.py -v -f <filename>

- regression of FPGA test suite

s25_regress.py --fpgaboard -f <filename>

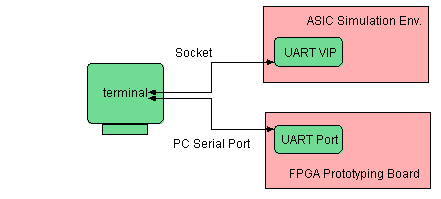

软硬件协同验证(Co-Verification)

很想拥有mentor的seemless,可是我没有。只好自力更生,自己开发一个co-verification的环境出来。

上图中terminal是一个用python开发出来的Command Line Interface(CLI)。它可以将处理器的程序编译成为二进制代码后通过Socket Inter Process Communication传送给仿真环境,仿真环境将接收来的数据作为UART的输入数据,芯片内置的firmware将通过UART接收来的程序数据放置到预先设定的RAM空间,然后再跳转到该空间开始执行相应的程序。当FPGA prototyping和它连接时,则需要将连接的方式改为PC的串口。

这样一个系统的优点是在芯片硬件开发的同时,driver/diagnostic/application软件可以并行开发,而不是必须等待FPGA board ready or real chip back,another advantage is that we can have almost unlimited copies of this development environment in simulation instead of limited copies of FPGA board which sometimes restricted us from putting more human resources into the software development when it becomes the critical path of the whole project.

FPGA code base simulation

In one terminal

cd sandbox/s25/SIM/verif/sim s25_run.py -c -w --fpga test_cover -s 1 -l

Here, -c means compile the code base, --fpga means use the fpga code base, -w means waveform will be dumped, -s 1 means use 1 as the random seed, -l means simulation log file will not be recorded. test_cover is just a test case name, it has no special meaning here, as the firmware is always hard-wired in sprom16kx32_init.v in sandbox/s25/SIM/fpga/rtl

In another terminal

cd sandbox/s25/SIM/verif/sim s25_cover.py

Inside the terminal of s25_cover.py, the command list should like below:

setup asic read 0xc2100 write 0xc2100 789 run 10000 exit

ToDO:

- change the read command to adjust the wait time according the baud rate, otherwise, some bogus error message will appear.

Project Management

cvs is adapted for revision control,Rational ClearQuest is adapted as issue/bug tracking tool

env user guide

FPGA Prototyping Env. Setup

The power supply of the target board is +5v, however, due to the bad quality of the DC regulator, the switch should pointer +12v, otherwise, the target board will not work properly, the LED display in the target board is dim.

IPPorter的bringup

- In root

cd /etc/rc.d/init.d ./ipporterd start

After this, you should be able to see s2c information from the LCD of IPPorter. If not, something wrong, you should disconnect the power supply and USB port, let the capacitor discharge for several minutes, then try again, normally you can see s2c information now.

- In normal User

s2c &

- Before turn off IPPorter

cd /etc/rc.d/init.d ./ipporterd stop

For Prototype Navigator v Beta1.0.14, things need to be modified manually listed below:

- after Create Partition, you had to modify the pin name of global clock from PIO_O to PIO_CLK_O in fpga_bm.rpt in the folder of projDir/ace

before place & route, you need to copy the information of rom location constraint in ncf file located at projDir/ace/apsout/F3/*.ncf

- if you need to use ILA and need to probe internal signals of the design, you had to remove the path information in projDir/ace/fpga_bm/*.cell

- for a new project, you can copy the pin location information before Assign IO Connectors

- before download the bin file to IPPorter, you should run the bat file in the genBin directory, _init.v file will be generated in this step, by doing so, greatly speeding up firmware upgrade.

For Prototype Navigator v Beta 1.0.15,

- no manual change of fpga_bm.rpt

- signal names in top.pio changed to upper case

- a bug in software cause sram access error

- command to rebuild download bit/bin files

s25_s2c.py

- command to pack and archive the project files

s25_s2c.py --pack --name <filename> --path <project file folder>

- command to download an archived project files to IPPorter

s25_s2c.py --download <filename>

FPGA Testing

You should run a test at sandbox/s25/SIM/verif/sim, command to run a single test is

s25_run.py --fpgaboard <testcasename> --seed <random seed>

testcase is stored at sandbox/s25/SIM/verif/tests, generally, the name should start with fpga_, in each test case, testing program and the expected return value through uart should be specified.